Depending upon the type of engineer you ask the word test evokes a different notion of goals and expectations.

Engineers who work on the design of semiconductors test that their designs meet the specifications.

This can be done pre-silicon and naturally verified in-depth on silicon.

Engineers concerned with manufacturing of a product test to find defects and to verify performance.

Similar approaches can be taken by both engineers though there exist differences in the amount of time. To be cost effective, a manufacturing test must be completed in as short a time as possible. Let’s continue to compare and contrast design validation with manufacturing test.

Design Test

When designers test their designs technically they are validating the design prior to producing silicon. They accomplish this by using computer-based simulation tools which can validate at different abstraction levels:

- Formal verification proves the correctness of algorithms underlying a logic blocks function

- Logic validation checks a functional blocks operations looking functional operation

- Gate level simulation checks the operation of 1’s & 0’s via a logical block function

- Transistor simulation checks a circuit operation examining voltage levels, currents with respect to time or frequency domain

Manufacturing Test

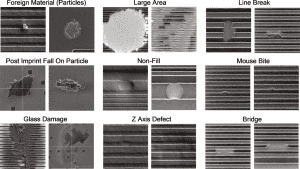

When manufacturing engineers test their products technically they are failing a product that is unable to functional as specified in a customer system. Defects often change a circuit’s structure so that the behavior is obviously different. There exist defects in which the change in circuit structure exhibits a more nuanced behavior. This requires more sophisticated methods. Naturally, if the product has been manufactured outside the process window (typically 4-sigma process window assumed) these parts need to be failed. Underlying manufacturing test there exists an assumption that the design has been validated. A manufacturing test could not detect the Intel Pentium Floating Point Error in 1994 (see references below for additional info).

Engineers perform manufacturing test with a combination of Automatic Test Equipment (ATE) and Design For Test (DFT) circuitry. Device Under Test (DUT) Approaches include:

- Operational Test: place the DUT in a system and run software.

- Functional Test: functionally apply operations on the DUT and verify the correct output in forms of 1’s & 0’s; verify that the analog circuit has a specified voltage/timing/current/frequency response.

- Structural Test: apply 1’& 0’s to the DUT to verify that the transistors are present and correctly connected or execute a test on an analog circuit which verifies no defects that would impact performance specs.

- Alternative Test: for digital test, apply 1’s and 0’s and measure power supply current (IDDQ testing); analog test, test with a signal that doesn’t represent normal input signals.

Test and Design versus Manufacturing

For those that like tables I have composed a table that provides more illustrative examples.

| Test | Arithmetic Logic Unit (ALU) Multiplier Example | SERDES interface like PCI Express 2.0 |

| Design validation | Multiple all possible numbers and check results | Simulate the SERDES interface with system transmission lines and measure Bit Error Rate (BER) |

| Operational | Run QUAKE on the part when in a System | Run an application that sends traffic on the SERDES interface, measure BER |

| Functional | Run instructions for Adding numbers | Run instructions on the DUT that send traffic to the SERDES device and measure Data Eye characteristics |

| Structural | apply structural tests (supported with DFT) that check all transistors present and connected correctly | Execute an external loopback test at speed |

| Alternative tests: | Testing a circuit in a non-conventional manner. Example IDDQ testing, for CMOS only | Modify the transmitter strength during an external loopback test to provide a reduced data eye to the receiver |

Test Expectations- How Much Escapes?

Manufacturing test may not be perfect; customer quality expectations vary. If they are only accepting a few 100 units than they can manage with a lower quality level. Their expectations change with the product volume they receive as well as the end use of the application. The quality of a manufacturing test is specified by the escapes measured in parts per million (ppm). In general, this is called Defects Per Million (DPM), though companies may call it by a different name. While a young engineer at IBM someone told me the story behind IBM’s term- Shipped Product Quality Level (SPQL). An executive declared “We don’t ship defective product,” clearly someone with a marketing mindset. SPQL reminds me of the telecommunications spec; Grade of Service (GOS) which quantified the number of dropped calls/calls that couldn’t go through. Framing is everything as Tversky and Kahneman have shown in numerous psychological cognitive research. Pardon my digression, let’s get back to expectations.

Different industries that use electronics have specific expectations on quality and reliability of the electronics used in the end user systems. If we stick with DPM, a DPM value needs to include defects that fail in the system right away and defects that fail during the system operation lifetime- reliability. In computer systems used in normal business differ in up-time expectations than the server systems used in high-speed financial transactions. Quality wise most microprocessors commit to a 300-500 DPM. Systems that go up into the stratosphere and all the way out into space must mitigate the impact of radiation. The reliability of the electronics in a home appliance differs from an automobile. Mission critical systems like airplanes and satellites need to be immune to radiation. Aviation systems use triple redundancy to assure safe operation of the complexities of flying a modern airplane.

Electrical circuitry types have each have had their own evolutionary path on test approaches. The next few posts will provide introductions to logic, memory and analog testing. Let me know which test approaches you would like to learn more about and I will follow-up with some Mastery 2 articles.

Meanwhile remember testing takes time and thoughtful application,

Anne Meixner, PhD

Additional Reading:

The Intel Floating Point Error is described in this Wikipedia article. For those interested in a chronology of events read this post.

A recent article from Semiconductor engineering addressed current issues on quality and some of the shift in thinking on defects.

Understanding the concept of framing can be very useful when you wish to persuade others. The Israeli psychologists Daniel Kahneman and Amos Tversky collaborated on research that examined thinking processes.

Ask a question or send along a comment.

Please login to view and use the contact form.

Ask a question or send along a comment.

Please login to view and use the contact form.

Leave a Reply