Just One More Thing

Memory circuits store 1’s and 0’s for you so that you can retrieve them later. The 1/0’s can represent data or instructions.

Today, no computing device operates without some memory. Memory devices store pictures, music, documents. How many USB (Unified Serial Bus) memory sticks do you have scattered on your desk?

Semiconductor memory comes in many flavors: Dynamic Random Access Memory (DRAM), Static Random Access Memory (SRAM), Read Only Memory (ROM), Erasable Programmable Memory (EPROM), NAND/NOR Memory (a.k.a. Flash), Solid State Drive (SSD). Without power volatile memories like SRAM and DRAM lose their stored values. Non-Volatile memories retain their stored value when power is absence.

Stuck at Fault Model Not Sufficient for Memory Test

As memory just stores 1’s and 0’s what could be so hard about it testing it? You apply the stuck at fault model and done! With this introductory article I want you to leave with an appreciation of the nuanced nature of memory test. I will use CMOS (Complementary Metal Oxide Silicon) SRAM to illustrate.

Remember the stuck at fault model was developed for testing logic circuits. Slightly removed from the physical implementation of the circuitry—tis technology agnostic. This abstraction quickly breaks for memory circuits. As a starting point let’s apply the S@ model. The test would consist of:

Write a 1, then read a 1, if you get a 0 you have a fail.

Write a 0, then read a 0, if you get a 1 you have a fail.

Voila, Fini!

Oh one more thing, there’s that write and read operation. Specific circuitry performs that function. Also, read/write operations are not performed 1 bit at a time, but a row of bits at time. Address circuitry connects the read/write circuitry to that row in memory. How many bits are there? Well that depends if it is a stand-alone memory embedded. Sizes are typically on order of 512 megabytes or more.

Tally the Memory Parts to Test

First let’s look at memory from top view at architecture and drill down to the transistor level description. Along the way you can tally the circuitry that requires to be tested.

Memory is organized in blocks and a grid system in which there are columns and rows. Address circuitry connects the row of bits (often organized in bytes- 8 bits) to the read and write circuitry. Registers hold the bit values to be written or read.

Let’s start the Tally:

- Address circuitry- Did you write to the correction location? Does it matter if it is the wrong location as long as it’s consistent?

- Read circuitry- Did it read correctly within time allowed? How could you tell the difference between a faulty read circuitry and a faulty bit?

- Write circuitry- Did it write the correct value within the time allowed? How long does it take to write the opposite value? How could you tell the difference between a faulty write circuitry and a faulty bit?

- What about those storage buffers?

- Bit cells- is the bit faulty?

No BIT is an Island

No woman is an island, the same holds true for a bit cell. They are surrounded by neighbors (except the ones on the edges- though physically they are not the last row or column). Consider a 3×3 array. Neighbors north, south and west are immediate and then neighbors on the diagonal. Columns of Bit and Bit bars connect multiple cells in the North South direction. A row addresses connect multiple cells in the East West Direction. Bit and Bitbar lines are shared with north and south neighbors.

In the presence of defects neighbors can lead to interactions which are often described as pattern sensitive faults. Consider the following pattern in which a bit cell with a zero is surrounded by 1’s. That bit could be influenced to be a 1.

1 1 1

1 0 1

1 1 1

Why is it like this, well this relates to how densely packed the cells are physically.

Single Cell Test Perspective

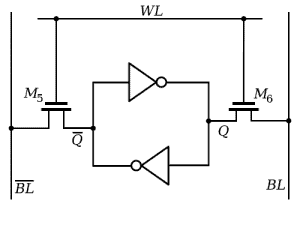

Now let’s look at a single bit cell. One way of representing it is as two inverters connected to one another.

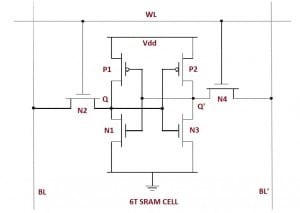

More often the transistor level representation provides some further insight. Six transistors compose the most often used SRAM cell; therefore, called 6-T cell.

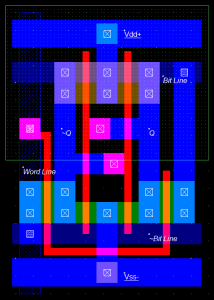

And as Columbo would say “Just one more thing.” Integrated circuit memory devices pack a lot of storage in their area. For a semiconductor process the design rules for memory circuits are more aggressive than they are for logic circuits. This is because the shapes are highly regular and can be optimized for the process node while logic circuit is much more random. Due to the higher density memory cells exhibit higher sensitivity to spot defect. The physical layout provides you with the lowest level of a memory cell. The implementation will vary according to the process node and design style. Below shows you an example.

Size, Density, Timing make Memory Test Hard

The S@ fault model lacks the ability to model interactions between cells. These interactions have resulted in numerous algorithm test patterns that need to be supplied. Timing related faults occur—how long between the next read/write to the same cell. Memory size dictates the number of bits that need to be tested with all these patterns. However, the very regular nature of memory cell design and architecture can lead to some advantages when developing a test solution.

What’s the just one more thing for you when you think about memory test? Do you want to know more about DRAM and SRAM testing? Or would you be more interested into delving into the non-volatile memory? Have you heard about a specific test that you want to know about? Curious about DFT solutions? Let me know and I will follow-up with an article addressing your specific needs.

Meanwhile remember testing takes time and thoughtful application,

Anne Meixner, PhD

Additional Reading:

Wikipedia has several articles on Memory design including Memory Cell, SRAM and DRAM

Several books on memory testing can be found on Amazon

Testing Semiconductor Memories: Theory and Practice by A. J. Van De Goor. I have used this book and I met the author when he did a summer visiting professor at Intel. It’s the classic text on testing memories.

High Performance Memory Testing: Design Principles, Fault Modeling and Self-Test by R. Dean Adams. I met Dean over 10 years ago at a test conference when he worked for IBM. While I have not read his book, I know that he brings his many years as a designer to this subject.

Semiconductor Memories: Technology, Testing, and Reliability by Ashok K Sharma. I have not read this book, but I thought for the reliability engineering audience this might be a good reference.

Ask a question or send along a comment.

Please login to view and use the contact form.

Ask a question or send along a comment.

Please login to view and use the contact form.

Memory is an integral part of the computer system. RAM required for the better performance of the system. The thing which makes memory testing hard is size density and timing.