What happens when you power up an electronics device with clocked circuits?

Well you have a clock running and you have clocked circuit elements, also known as sequential circuits. Latches, registers, basically any “memory” element. What could interfere with testing?

Do you know the state of that “memory element” when you start?

Heck No!

That’s a problem.

A Brief Overview of Sequential and Clocked Circuits

Recall that in the previous articles on digital logic testing dealt only with combinational circuits- no memory elements. In combinational logic the 1’s and 0’s flow in one direction. Most memory elements require feedback in the circuit similar to an SRAM cell.

With sequential circuits the state of the memory element is impacted by current and previous state. These memory elements can be asynchronous or synchronous. With an asynchronous memory element, the state changes based solely upon a change in the inputs. A synchronous memory element can only change at when the control signal arrives. Often a clock provides the control signal. Let’s explore some common on memory elements common in digital circuitry.

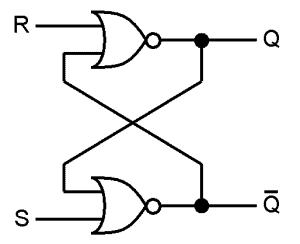

- Latch: Set and Reset Latch SR latch, can be constructed by a pair of cross-coupled NORs.

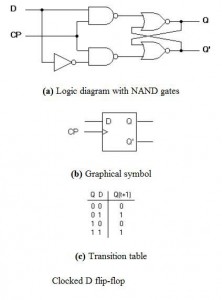

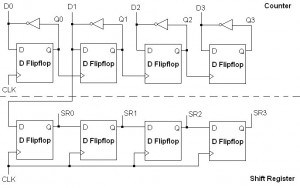

- D Flip-Flop: A Data/Delay Flip-Flap captures the D value at a prescribed portion of a clock, often the rising clock edge. They can also have the ability to set or reset the Flip-Flop State.

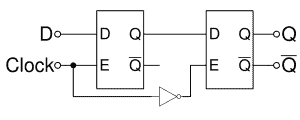

- Master-Slave D Flip-Flop: Two D Flip-Flops connected but with opposite clocks. This provides a stable transfer of state.

- Shift Register: Composed of a series of D Flip-Flops

Why Use Clocked Sequential Circuits?

Having the ability to remember a state can be useful during computation. Just think of the basic calculator with MS- Memory Store, M+- Add to Memory, MR- Memory Recall. These demonstrates an asynchronous computation- you control the computation.

In a computer with multiple moving parts, a clock signal synchronizes the communication between the moving parts. If you didn’t add a clock signal to the memory element you might have the moving parts conflict.

Clocked digital design has existed for decades in computer design. While you can compute with asynchronous elements it requires the adherence to communication protocol to handle the communication between different circuit blocks.

Address the Unknowns

Let’s get back to the very beginning. With feedback of logic signals there’s a state-stored. However, when you power up the device under test (DUT) the states of the sequential circuits are unknown.

Clearly you need to address the unknowns, i.e. change them to a known state. Several means exist to address this. As noted earlier, some Flip-flops have reset function, you could just yank all the resets together somehow. Another option- deliberately set the state in each latch to one that will assist with the test pattern you want to apply.

Hmmm how so? Would not such approaches result in adding circuits just so you can test them? Is it worth the effort and cost to do so?

Hmmm how so? Would not such approaches result in adding circuits just so you can test them? Is it worth the effort and cost to do so?

I have lead you down the path to door called Design For Test (DFT). A common DFT technique used for sequential circuits that engineers rely upon is called Scan-Based design. Though, before you learn about Scan I want to provide a primer on DFT in general. There’s a large castle behind that door, so prepare for several building blocks to lead you up to the top of the turret.

What is the major take-away for you after reading this introduction?

Meanwhile remember testing takes time and thoughtful application,

Anne Meixner, PhD

Additional Reading:

ECE tutorials provides succinct explanations of flip-flops. I have noticed that there exists some inconsistency between the definition that I’m using for latch vs flip-flop and theirs. This happens, in the end you need to look at the circuit diagram and not the name to know how something will behave.

You may have noticed I hedged that clocks are a requirement for computer design. Asynchronous computing does have its fans as it saves the time and effort of routing a clock signal all over the place. Hence it saves on power and also makes an integrated circuit less noisy. At some point I can discuss asynchronous circuits and the test challenge. Meanwhile if you’re curious check out the Asynchronous Research Center at Portland State University. Marly Roncken and Ivan Sutherland have been developing the work.

Ask a question or send along a comment.

Please login to view and use the contact form.

Ask a question or send along a comment.

Please login to view and use the contact form.

The article is very informative and gives some very useful knowledge of the clocked circuit. In the world of digital after making develop a thing it is very important to test whether it is working properly or not. Keep posting this kind of information.